Reversible Computing Architectures

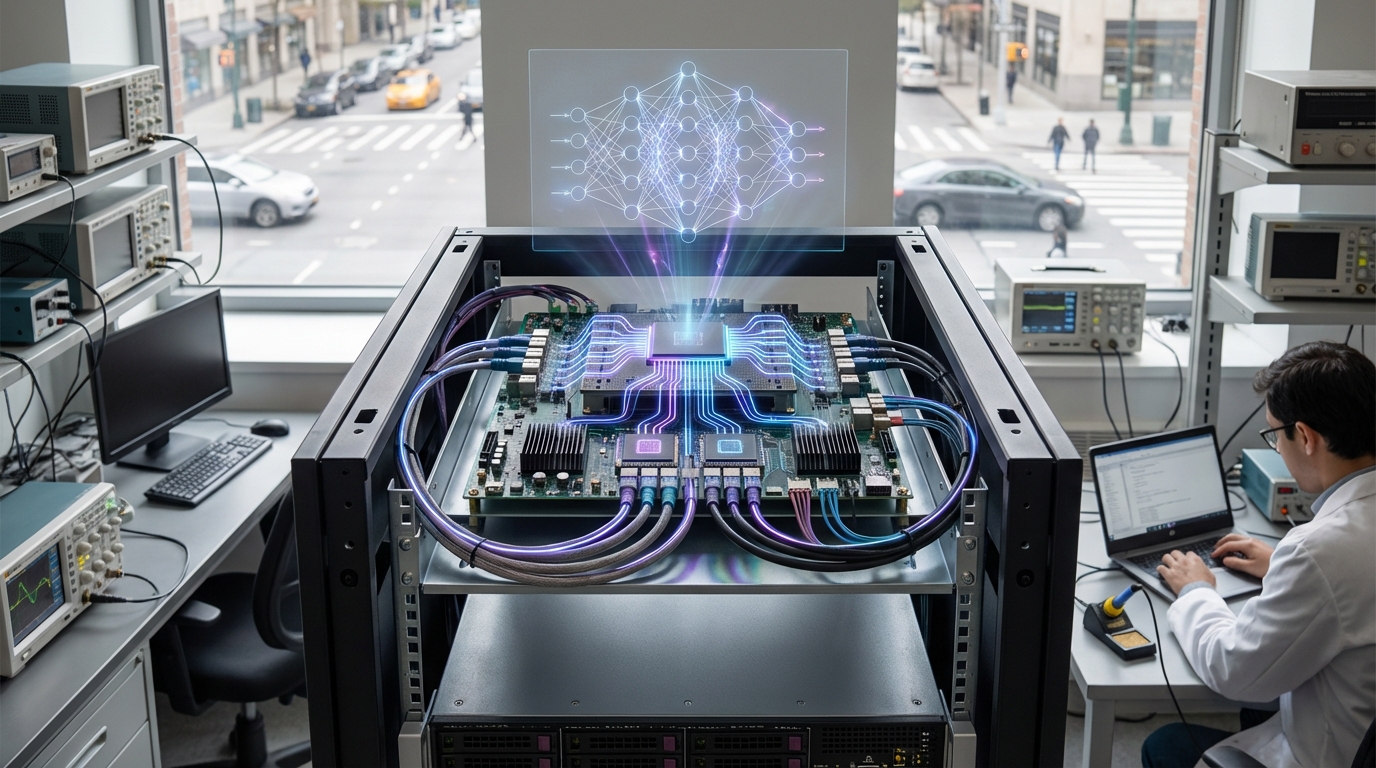

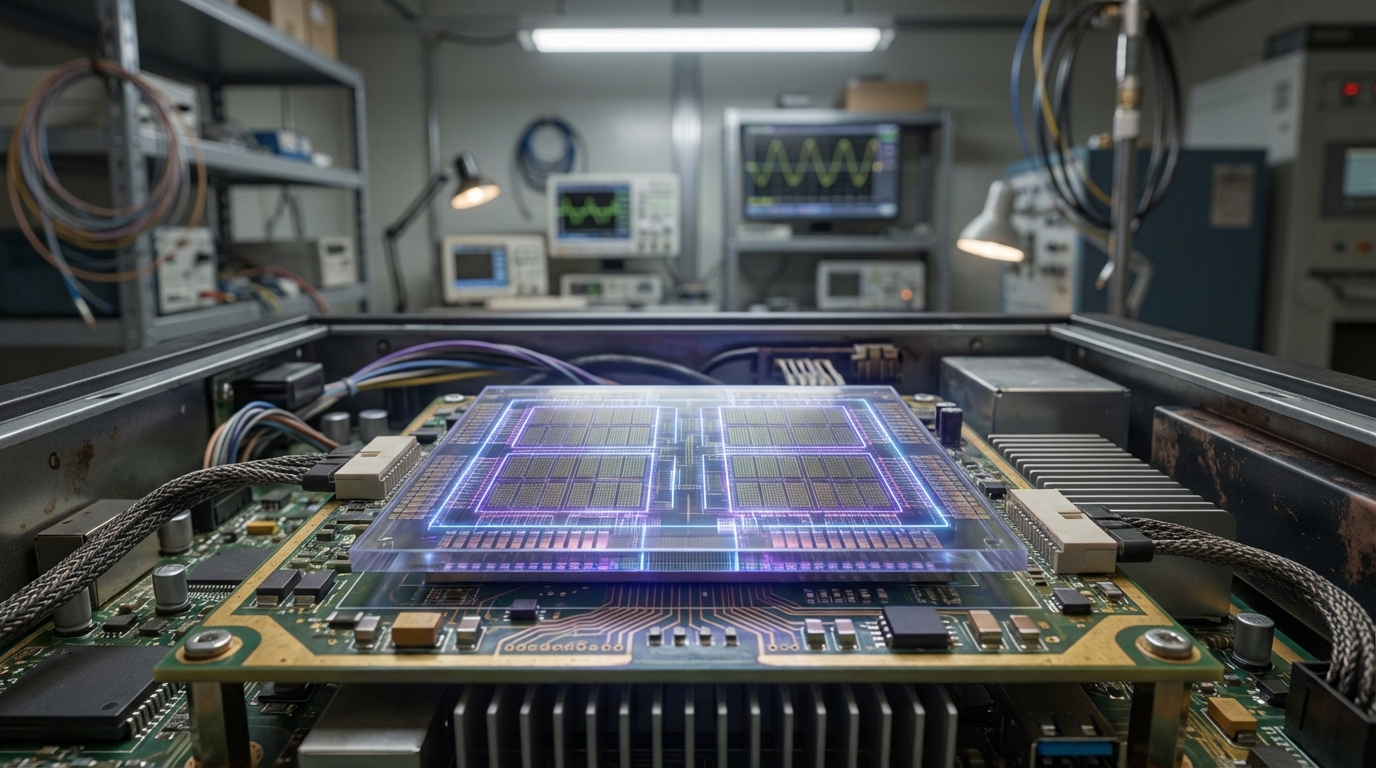

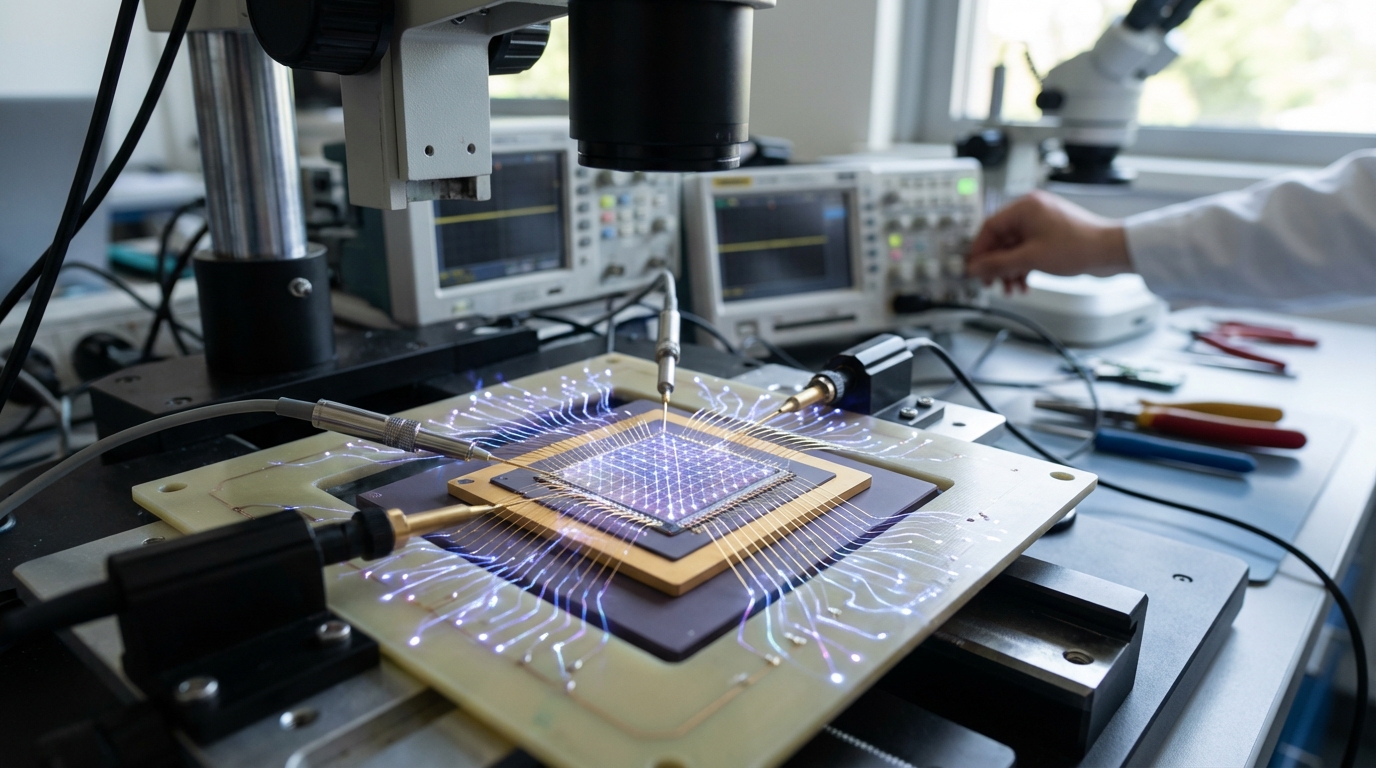

Reversible computing architectures use logic gates and circuits that can run backwards, theoretically allowing energy to be recovered and reused rather than dissipated as heat. These systems use adiabatic (slow, energy-conserving) switching and reversible logic gates that don't erase information, potentially enabling computation with near-zero energy dissipation. The approach is based on the physical principle that information erasure is what requires energy in computation.

This innovation explores the theoretical limits of energy-efficient computing, potentially offering a pathway to ultra-efficient AI systems that could train and run large models with minimal energy consumption. While traditional computing is fundamentally irreversible (erasing information creates entropy and requires energy), reversible computing seeks to minimize or eliminate information erasure. Research institutions are investigating these concepts, though practical implementations remain highly experimental.

The technology is particularly significant given the enormous energy consumption of training and running large AI models, which has become both an economic and environmental concern. If reversible computing could be practically realized, it could enable sustainable AI at scale. However, the technology faces fundamental challenges including the need for extremely slow, carefully controlled operations, the complexity of reversible logic design, and the practical difficulty of recovering energy. The approach remains largely theoretical, with practical applications likely decades away if they materialize at all.

Related Organizations

A US Department of Energy lab actively researching adiabatic logic circuits and reversible computing to overcome thermodynamic limits in microelectronics.

Japan · University

Leading research institution for Adiabatic Quantum-Flux-Parametron (AQFP) logic, a superconducting reversible logic family.

United States · University

Home to the Reversible Computing research group led by Dr. Michael Frank, a pioneer in the theory and engineering of reversible logic.

Long-standing leader in neuro-symbolic AI, combining neural networks with logical reasoning for enterprise applications.

Japan · Government Agency

Japanese national research institute working on superconducting electronics and adiabatic circuits for high-efficiency computing.

United States · Research Lab

Conducts research on superconducting computing architectures, including reversible logic designs for energy efficiency.

Conducts research on reversible logic synthesis and low-power VLSI design.

Research into spintronics and probabilistic computing which overlaps with reversible logic principles.

United States · Company

Developer of Digital-RF and superconducting microelectronics using Rapid Single Flux Quantum (RSFQ) logic.

Focuses on atomically precise manufacturing, a prerequisite for constructing theoretical reversible mechanical computing systems.