Chiplet & Advanced Packaging

Geography: Americas · North America · United States

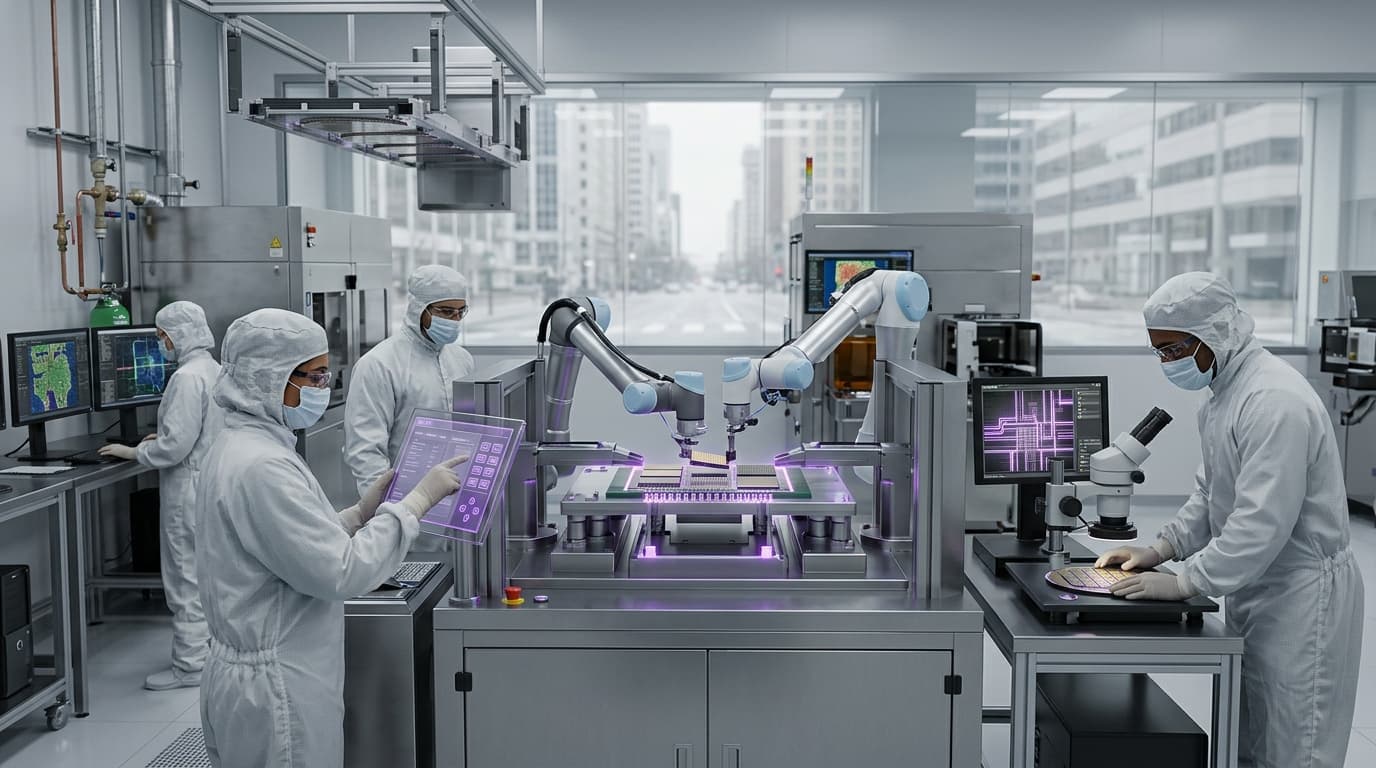

Chiplet architecture decomposes monolithic chips into smaller, specialized 'chiplets' that are interconnected using advanced packaging technologies like TSMC's CoWoS and Intel's Foveros. The Universal Chiplet Interconnect Express (UCIe) standard, backed by Intel, AMD, and ARM, enables interoperability between chiplets from different manufacturers. This allows mixing compute, memory, I/O, and AI accelerator chiplets from different process nodes.

Chiplets solve a fundamental scaling problem: as transistor shrinking slows, the economics of building ever-larger monolithic chips become prohibitive. By disaggregating functions, chiplets improve yield (smaller dies have fewer defects), enable specialization, and allow faster design cycles. The market is projected to reach $600 billion by 2031.

For the US, chiplet architecture reduces dependence on cutting-edge lithography — critical functions can use mature process nodes while only the compute core requires leading-edge fabrication. This aligns with CHIPS Act investments in advanced packaging facilities and could allow US-based assembly to add value even when wafer fabrication remains concentrated in Asia.