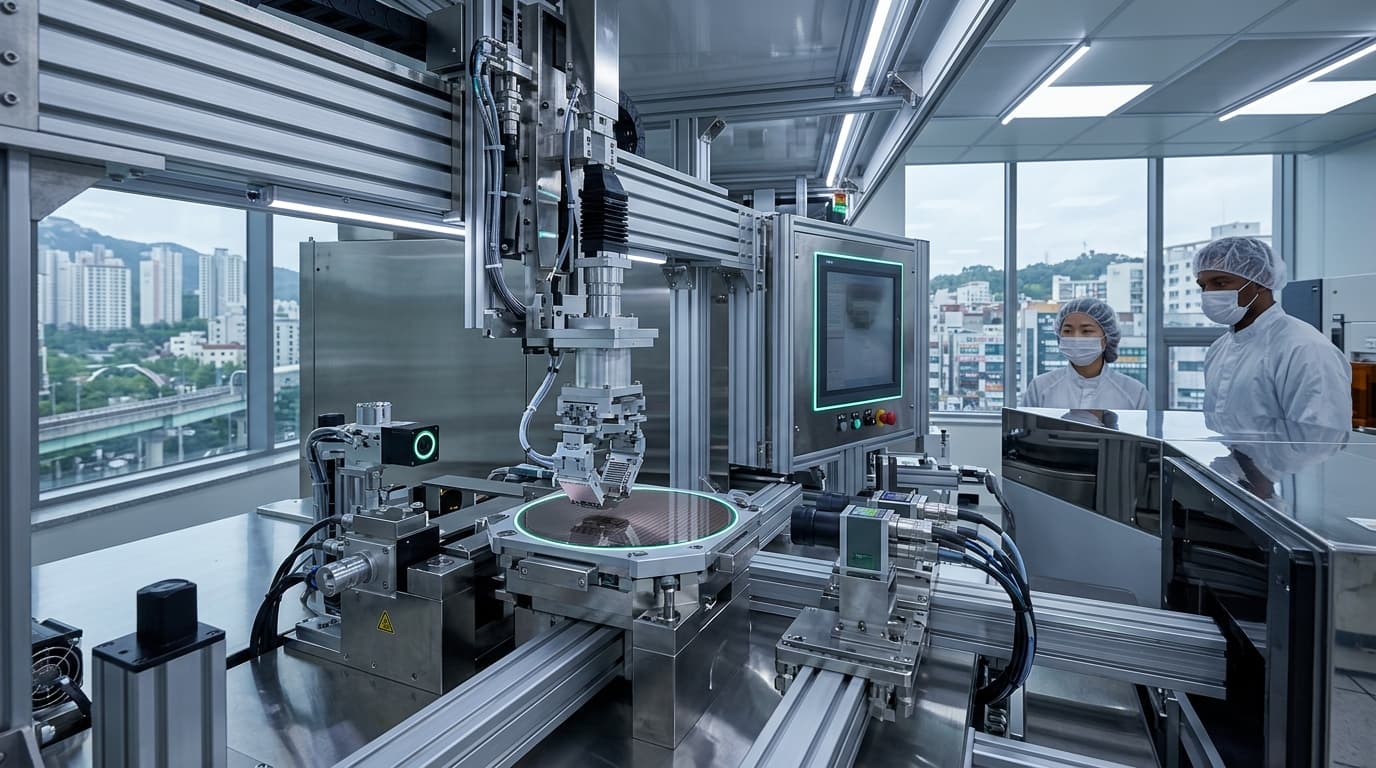

321-Layer NAND Flash

Geography: Asia Pacific · East Asia · South Korea

SK Hynix announced mass production of 321-layer 3D TLC NAND flash in 2024, surpassing Samsung's 236-layer and Micron's 232-layer products as the highest-stacking NAND chip in the world. The 321-layer design uses a string-stacking architecture that bonds two wafers together, each containing ~160 layers of memory cells.

More layers mean more storage density per chip, which directly reduces cost-per-gigabyte for SSDs and data center storage. The race to stack more NAND layers is fundamentally a manufacturing challenge — each additional layer increases the risk of defects, alignment errors, and yield loss. SK Hynix's ability to manufacture 321 layers at production-grade yields demonstrates world-leading vertical integration of deposition, etching, and bonding processes.

Samsung has since announced plans for 430+ layer NAND, keeping the competitive pressure intense within Korea itself. This intra-Korean competition — Samsung vs. SK Hynix — has been a primary driver of global memory technology advancement for two decades.