Advanced Semiconductor Packaging (CoWoS, Foveros)

Geography: Americas · North America · United States

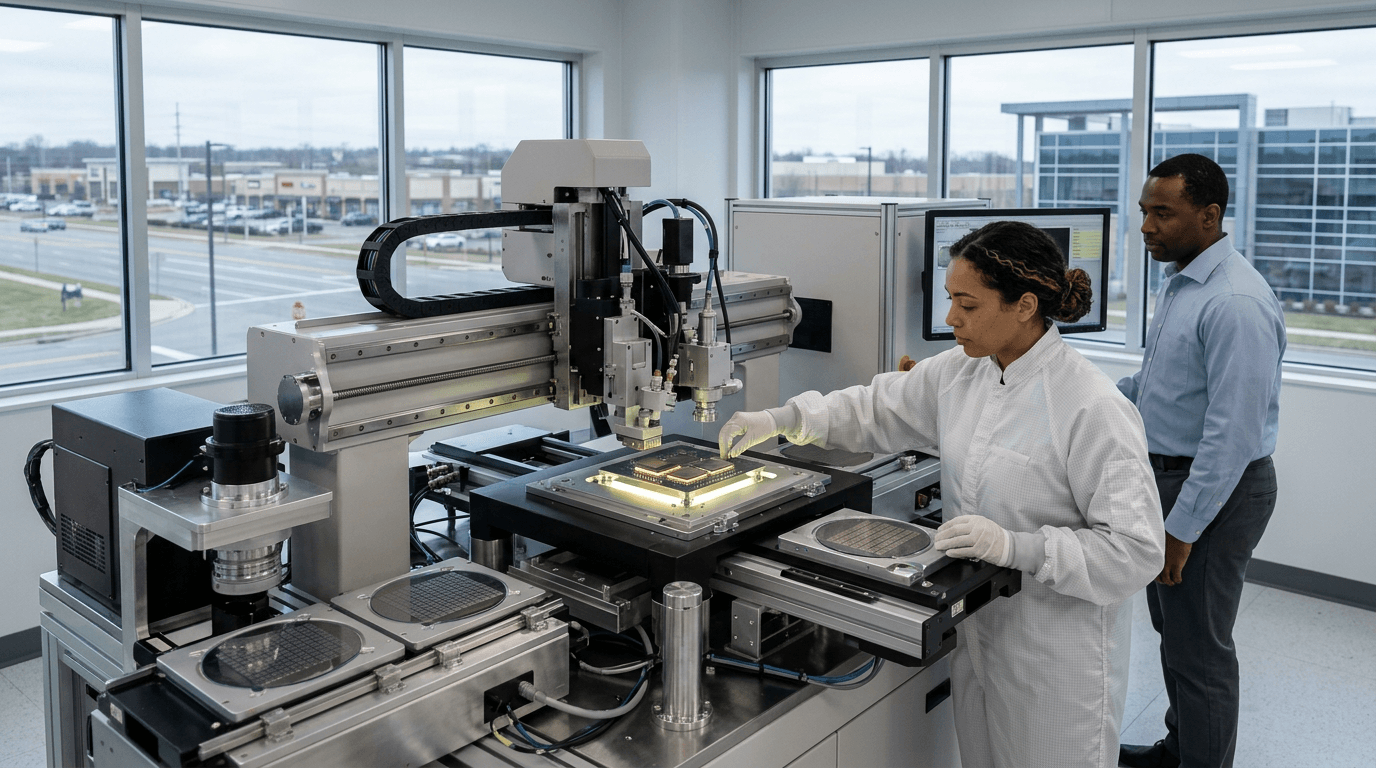

Advanced semiconductor packaging integrates multiple dies (chiplets, memory, interconnects) into a single package using technologies like TSMC's Chip-on-Wafer-on-Substrate (CoWoS) and Intel's Foveros. These packages combine compute chiplets with high-bandwidth memory (HBM) stacks, enabling the massive memory bandwidth that AI accelerators require. NVIDIA's H100 and B200 use CoWoS packaging.

Advanced packaging has become the critical bottleneck in AI chip supply — TSMC's CoWoS capacity limits how many AI GPUs can be produced, regardless of wafer fabrication capacity. This has made packaging technology as strategically important as lithography. The CHIPS Act includes specific funding for advanced packaging R&D and manufacturing facilities in the US.

Packaging innovation is where the US can build domestic capability without replicating TSMC's leading-edge wafer fabrication. Intel's US-based packaging facilities, combined with CHIPS Act-funded research, could create a domestic advanced packaging ecosystem that adds value even when bare dies are fabricated overseas.