Cryptographic Acceleration Chips

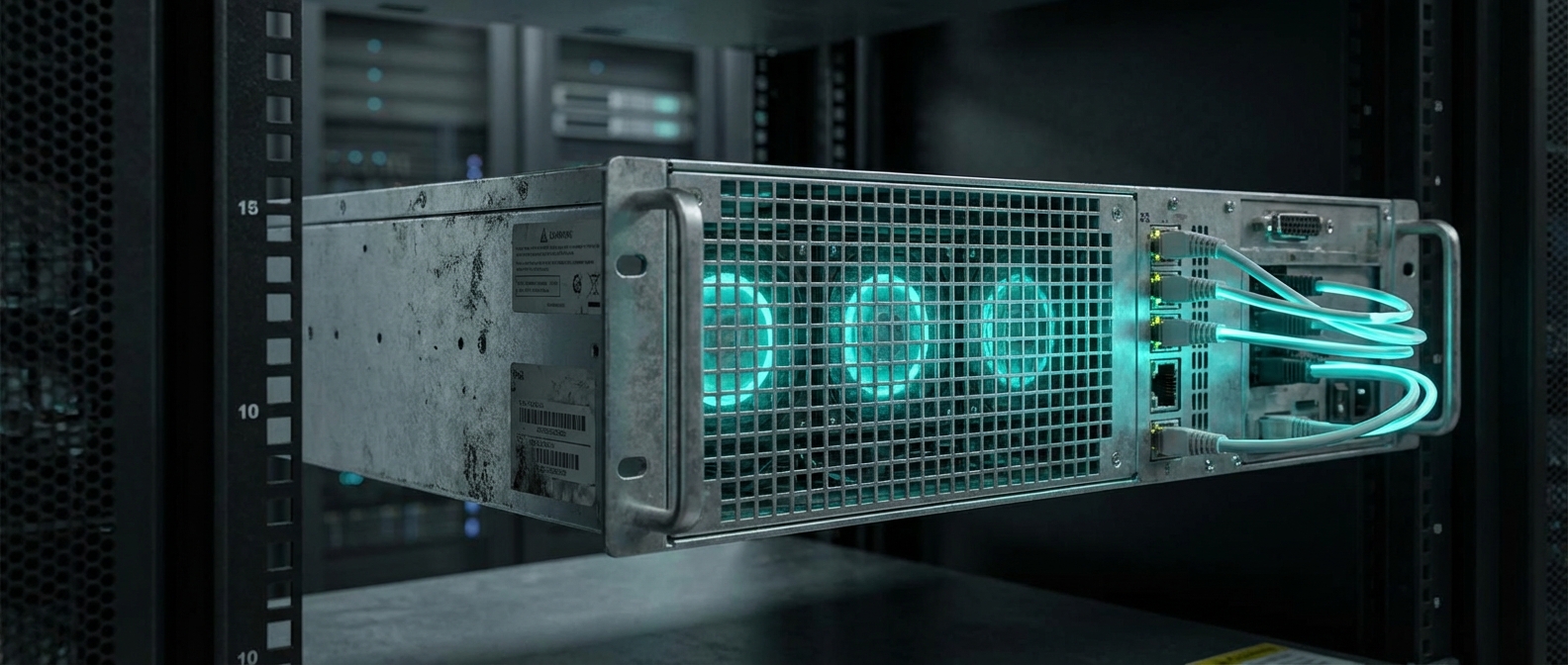

Cryptographic acceleration chips are specialized hardware including application-specific integrated circuits (ASICs) and neuromorphic computing cores that are explicitly optimized for computationally intensive cryptographic operations including ZK-SNARK/STARK proving (generating zero-knowledge proofs that verify computations without revealing the underlying data), multi-party computation (MPC, where multiple parties can compute functions over their inputs while keeping those inputs private), and homomorphic encryption (performing computations on encrypted data without decrypting it). In parallel, mature secure enclaves (protected execution environments) and hardware security modules (HSMs) already ship in payment terminals, phones, and custody infrastructure, enabling on-device key management, fast cryptographic proving, and wallet abstraction for secure, decentralized interactions at scale by offloading computationally expensive cryptographic operations to specialized hardware.

This innovation addresses the computational bottleneck in advanced cryptography, where operations like zero-knowledge proofs and homomorphic encryption are extremely computationally expensive on general-purpose processors, limiting their practical use. By creating specialized hardware, these chips can perform these operations orders of magnitude faster, making advanced cryptographic techniques practical for real-world applications. Companies and research institutions are developing these specialized chips.

The technology is essential for enabling practical use of advanced cryptographic techniques in blockchain, privacy-preserving computation, and secure systems, where specialized hardware makes these operations feasible. As cryptographic techniques become more important, specialized acceleration becomes increasingly valuable. However, ensuring security, managing costs, and achieving widespread adoption remain challenges. The technology represents an important evolution in cryptographic infrastructure, but requires continued development to achieve the performance and cost-effectiveness needed for widespread use. Success could enable practical deployment of advanced cryptographic techniques, but the technology must balance performance, cost, and security to achieve widespread adoption.

Related Organizations

Semiconductor company focusing on Zero Knowledge Proof hardware acceleration.

Hardware-accelerated cryptography for the blockchain industry.

Develops STARK-based scaling solutions for blockchain (StarkNet, StarkEx).

Develops the RDNA architecture with Ray Accelerators, powering ray tracing on PC and current-gen consoles (PS5, Xbox Series X).

Developing foundation models for robotics (Project GR00T) and vision-language models like VILA.